# Contents

| Digital C | ircuits                                      | 2 |

|-----------|----------------------------------------------|---|

| 2.1       | Binary Numbers                               | 3 |

| 2.2       | Binary Switch                                |   |

| 2.3       | Basic Logic Operators and Logic Expressions  |   |

| 2.4       | Truth Tables                                 | 7 |

| 2.5       | Boolean Algebra and Boolean Functions        | 8 |

| 2.5.1     | 1 Boolean Algebra                            | 8 |

| 2.5.2     |                                              |   |

| 2.5.3     |                                              |   |

| 2.6       | Minterms and Maxterms                        | 3 |

| 2.6.      | 1 Minterms1                                  | 4 |

| 2.6.2     | 2 * Maxterms1                                | 5 |

| 2.7       | Canonical, Standard, and non-Standard Forms1 |   |

| 2.8       | Logic Gates and Circuit Diagrams1            |   |

| 2.9       | Designing a Car Security System              |   |

| 2.10      | VHDL and Verilog for Digital Circuits        |   |

| 2.10      | 1122  code for  u = mpart if if  2  gate     |   |

| 2.10      |                                              |   |

| 2.10      | 0.3 VHDL code for a function                 | 4 |

| 2.10      |                                              |   |

| 2.10      | 0.5 Verilog code for a 3-input NOR gate2     | 5 |

| 2.10      | 8                                            |   |

| 2.11      | Summary Checklist                            |   |

| 2.12      | Problems                                     | 7 |

| Index.    |                                              | 4 |

# Chapter 2

# **Digital Circuits**

Our world is an analog world. Measurements that we make of the physical objects around us are never in discrete units, but rather in a continuous range. We talk about physical constants such as 2.718281828... or 3.141592.... To build analog devices that can process these values accurately is next to impossible. Even building a simple analog radio requires very accurate adjustments of frequencies, voltages, and currents at each part of the circuit. If we were to use voltages to represent the constant 3.14, we would have to build a component that will give us exactly 3.14 volts every time. This is again impossible; due to the imperfect manufacturing process, each component produced is slightly different from the others. Even if the manufacturing process can be made as perfect as perfect can get, we still would not be able to get 3.14 volts from this component every time we use it. The reason being that the physical elements used in producing the component behave differently in different environments, such as temperature, pressure, and gravitational force, just to name a few. Therefore, even if the manufacturing process is perfect, using this component in different environments will not give us exactly 3.14 volts every time.

To make things simpler, we work with a digital abstraction of our analog world. Instead of working with an infinite continuous range of values, we use just two values! Yes, just two values: 1 and 0, on and off, high and low, true and false, black and white, or however you want to call it. It certainly is much easier to control and work with two values rather than an infinite range. We call these two values a binary value for the reason that there are only two of them. A single 0 or a single 1 is then a **binary digit** or **bit**. This sounds great, but we have to remember that the underlining building block for our digital circuits is still based on an analog world.

This chapter provides the theoretical foundations for building digital logic circuits using logic gates, the basic building blocks for all digital circuits. In order to understand how logic gates are used to implement digital circuits, we need to have a good understanding of the basic theory of Boolean algebra, Boolean functions, and how to use and manipulate them. Most people may find Sections 2.5 and 2.6 on these theories to be boring, but let me encourage you to grind through it patiently, because if you do not understand it now, you quickly will get lost in the later chapters. The good news is that these two sections are the only sections in this book on theory, and I will try to keep them as short and simple as possible. You also will find that many of the Boolean theorems are very familiar, because they are similar to the algebra theorems that you have learned from your high school math class. As you can see from the microprocessor road map, this chapter affects all of the parts for building a microprocessor.

### 2.1 Binary Numbers

Since digital circuits deal with binary values, we will begin with a quick introduction to binary numbers. A bit, having either the value of 0 or 1, can represent only two things or two pieces of information. It is, therefore, necessary to group many bits together to represent more pieces of information. A string of *n* bits can represent  $2^n$  different pieces of information. For example, a string of two bits results in the four combinations: 00, 01, 10, and 11. By using different encoding techniques, a group of bits can be used to represent different information, such as a number, a letter of the alphabet, a character symbol, or a command for the microprocessor to execute.

The use of decimal numbers is quite familiar to us. However, since the binary digit is used to represent information within the computer, we also need to be familiar with **binary numbers**. Note that the use of binary numbers is just a form of representation for a string of bits. We can just as well use octal, decimal, or hexadecimal numbers to represent the string of bits. In fact, you will find that hexadecimal numbers are often used as a shorthand notation for binary numbers.

The decimal number system is a positional system. In other words, the value of the digit is dependent on the position of the digit within the number. For example, in the decimal number 48, the decimal digit 4 has a greater value than the decimal digit 8 because it is in the tenth position, whereas the digit 8 is in the unit position. The value of the number is calculated as  $(4 \times 10^1) + (8 \times 10^0)$ .

Like the decimal number system, the binary number system is also a positional system. The only difference between the two is that the binary system is a base-2 system, and so, it uses only two digits, 0 and 1, instead of ten. The binary numbers from 0 to 15 (decimal) are shown in Figure 2.1. The range from 0 to 15 has 16 different combinations. Since  $2^4 = 16$ , therefore, we need a 4-bit binary number (i.e., a string of four bits) to represent this range.

When we count in decimal, we count from 0 to 9. After 9, we go back to 0, and have a carry of a 1 to the next digit. When we count in binary numbers, we do the same thing, except that we only count from 0 to 1. After 1, we go back to 0 and have a carry of a 1 to the next bit.

The decimal value of a binary number can be found just like that for a decimal number, except that we raise the base number 2 to a power rather than the base number 10 to a power. For example, the value for the decimal number 658 is

$$658_{10} = (6 \times 10^2) + (5 \times 10^1) + (8 \times 10^0) = 600 + 50 + 8 = 658_{10}$$

Similaly, the decimal value for the binary number  $1011011_2$  is

$$1011011_2 = (1 \times 2^6) + (0 \times 2^5) + (1 \times 2^4) + (1 \times 2^3) + (0 \times 2^2) + (1 \times 2^1) + (1 \times 2^0)$$

$= 64 + 16 + 8 + 2 + 1 = 91_{10}$

To get the decimal value, the least significant bit (in this case, the rightmost 1) is multiplied with  $2^0$ . The next bit to the left is multiplied with  $2^1$ , and so on. Finally, they are all added together to give the value  $91_{10}$ .

Notice the subscript 10 in the decimal number  $658_{10}$ , and the 2 in the binary number  $1011011_2$ . This subscript is used to denote the base of the number whenever there might be confusion as to what base the number is in.

| Decimal | Binary | Octal | Hexadecimal |

|---------|--------|-------|-------------|

| 0       | 0000   | 0     | 0           |

| 1       | 0001   | 1     | 1           |

| 2       | 0010   | 2     | 2           |

| 3       | 0011   | 3     | 3           |

| 4       | 0100   | 4     | 4           |

| 5       | 0101   | 5     | 5           |

| 6       | 0110   | 6     | 6           |

| 7       | 0111   | 7     | 7           |

| 8       | 1000   | 10    | 8           |

| 9       | 1001   | 11    | 9           |

| 10      | 1010   | 12    | А           |

| 11      | 1011   | 13    | В           |

| 12      | 1100   | 14    | С           |

| 13      | 1101   | 15    | D           |

| 14      | 1110   | 16    | E           |

| 15      | 1111   | 17    | F           |

Figure 2.1 Numbers from 0 to 15 in binary, octal, and hexadecimal number systems.

Converting a decimal number to its binary equivalent can be done by successively dividing the decimal number by 2 and keeping track of the remainder at each step. Combining the remainders together (starting with the last one) forms the equivalent binary number. For example, using the decimal number 91, we divide it by 2 to get 45 with a remainder of 1. Then we divide 45 by 2 to get 22 with a remainder of 1. We continue in this fashion until the end as shown here.

$$2 \begin{array}{|c|c|c|} 2 & 91 & 1 \\ 2 & 45 & 1 \\ 2 & 22 & 0 \\ 2 & 11 & 1 \\ 2 & 5 & 1 \\ 2 & 2 & 0 \\ 1 & & \\ \end{array}$$

Least significant bit = 1011011

$$= 1011011$$

Concatenating the remainders together, starting with the last one (most significant bit) results in the binary number  $1011011_2$ .

Binary numbers usually consist of a long string of bits. A shorthand notation for writing out this lengthy string of bits is to use either octal or hexadecimal numbers. Since the octal system is base-8 and the hexadecimal system is base-16 (both of which are a power of 2), a binary number can be converted easily to an octal or hexadecimal number, or vice versa.

**Octal** numbers only use the digits from 0 to 7 for the eight different combinations. When counting in octals, the number after 7 is 10 as shown in Figure 2.1. To convert a binary number to octal, we simply group the bits into groups of threes, starting from the right (least significant bit). The reason for this is because  $8 = 2^3$ . For each group of three bits, we write the equivalent octal digit for it. For example, the conversion of the binary number 1110011<sub>2</sub> to the octal number 163<sub>8</sub> is shown here.

$$\frac{001}{1} \ \frac{110}{6} \ \frac{011}{3}$$

Since the original binary number has seven bits, we need to extend it with two leading 0's to get three bits for the leftmost group. Note that when we are dealing with negative numbers, we may require extending the number with leading 1's instead of 0's.

Converting an octal number to its binary equivalent is just as easy. For each octal number, we write down the equivalent three bits. These groups of three bits are concatenated together to form the final binary number. For example, the conversion of the octal number  $5724_8$  to the binary number  $101111010100_2$  is shown here.

The decimal value of an octal number can be found just like that for a binary or decimal number, except that we raise the base number 8 to a power instead of the base number 2 or 10 to a power. For example, the octal number  $5724_8$  has the value:

$$5724_8 = (5 \times 8^3) + (7 \times 8^2) + (2 \times 8^1) + (4 \times 8^0) = 2560 + 448 + 16 + 4 = 3028_{10}$$

**Hexadecimal** numbers are treated basically the same way as octal numbers except with the appropriate changes to the base. Hexadecimal (or hex for short) numbers use base-16, and thus require 16 different digit symbols, as shown in Figure 2.1. Converting binary numbers to hexadecimal numbers involves grouping the bits into groups of fours since  $16 = 2^4$ . For example, the conversion of the binary number  $11011011011_2$  to the hexadecimal number  $6DB_{16}$  is shown below. Again, we need to extend it with a leading 0 to get four bits for the leftmost group.

$$\frac{0110}{6} \quad \frac{1101}{D} \quad \frac{1011}{B}$$

To convert a hex number to a binary number, we write down the equivalent four bits for each hex digit, and then concatenate them together to form the final binary number. For example, the conversion of the hexadecimal number  $5C4A_{16}$  to the binary number  $0101110001001010_2$  is shown here.

The following example shows how the decimal value of the hexadecimal number C4A<sub>16</sub> is evaluated.

$$C4A_{16} = (C \times 16^{2}) + (4 \times 16^{1}) + (A \times 16^{0})$$

$$= (12 \times 16^{2}) + (4 \times 16^{1}) + (10 \times 16^{0})$$

$$= 3072 + 64 + 10 = 3146_{10}$$

#### 2.2 Binary Switch

Besides the fact that we are working only with binary values, digital circuits are easy to understand because they are based on one simple idea of turning a switch on or off to obtain either one of the two binary values. Since the switch can be in either one of two states (on or off), we call it a **binary switch**, or just a **switch** for short. The switch has three connections: an input, an output, and a control for turning the switch on or off, as shown in Figure 2.2. When the switch is opened, as in Figure 2.2(a), it is turned off, and nothing gets through from the input to the output. When the switch is closed, as in Figure 2.2(b), it is turned on, and whatever is presented at the input is allowed to pass through to the output.

Figure 2.2 Binary switch: (a) opened or off; (b) closed or on.

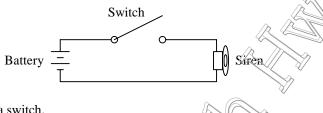

Uses of the binary switch idea can be found in many real-world devices. For example, the switch can be an electrical switch with the input connected to a power source and the output connected to a shown in Figure 2.3.

Figure 2.3 A siren controlled by a switch.

When the switch is closed, the siren turns on. The usual convention is to use a 1 to mean "on" and a 0 to mean "off." Therefore, when the switch is closed, the output is a 1 and the siren will turn on. We can also use a variable, x, to denote the state of the switch. We can let x = 1 to mean the switch is closed and x = 0 to mean the switch is opened. Using this convention, we can describe the state of the siren S in terms of the variable x using a simple logic expression. Since S = 1 if x = 1 and S = 0 if x = 0, we can write

This logic expression describes the output *S* in terms of the input variable *x*.

# 2.3 Basic Logic Operators and Logic Expressions

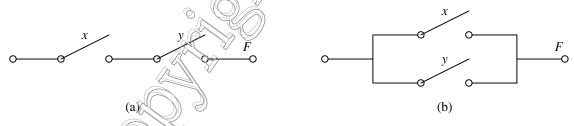

Two binary switches can be connected together either in series or in parallel, as shown in Figure 2.4.

Figure 2.4 Connection of two binary switches: (a) in series; (b) in parallel.

If two switches are connected in series, as in Figure 2.4(a), then both switches have to be on in order for the output F to be 1. In other words, F = 1 if x = 1 and y = 1. If either x or y is off, or both are off, then F = 0. Translating this into a logic expression, we get

$$F = x$$

AND  $y$

Hence, two switches connected in series give rise to the logical AND operator. In a Boolean function (which we will explain in more detail in Section 2.5), the AND operator is denoted either with a dot ( $\bullet$ ) or no symbol at all. Thus, we can rewrite the above expression as

$F = x \bullet y$

or simply

If we connect two switches in parallel, as in Figure 2.4(b), then only one switch needs to be on in order for the output *F* to be 1. In other words, F = 1 if either x = 1, or y = 1, or both *x* and *y* are 1's. This means that F = 0 only if both *x* and *y* are 0's. Translating this into a logic expression, we get

and this gives rise to the logical **OR** operator. In a Boolean function, the OR operator is denoted with a "plus" symbol (+). Thus, we can rewrite the above expression as

F = x + y

F = x OR y

In addition to the AND and OR operators, there is another basic logic operator—the **NOT** operator, also known as the **INVERTER**. Whereas, the AND and OR operators have multiple inputs; the NOT operator has only one input and one output. The NOT operator simply inverts its input, so a 0 input will produce a 1 output, and a 1 becomes a 0. In a Boolean function, the NOT operator is denoted either with an "apostrophe" symbol (') or a "bar" on top ( $\bar{}$ ) as in

or

When several operators are used in the same expression, the precedence given to the operators are (from highest to lowest) NOT, AND, and OR. The order of evaluation can be changed by means of using parenthesis. For example, the expression

F = xy + z'

F = x(y + z)'

means (x AND y) OR (NOT z), and the expression

means x AND (NOT (y OR z)).

#### 2.4 Truth Tables

The operation of the AND, OR, and NOT logic operators can be described formally by using a **truth table**, as shown in Figure 2.5. A truth table is a two-dimensional array where there is one column for each input and one column for each output (a circuit may have more than one output). Since we are dealing with binary values, each input can be either a 0 or a 1. We simply enumerate all possible combinations of 0's and 1's for all the inputs. Usually, we want to write these input values in the normal binary counting order. With two inputs, there are  $2^2$  combinations giving us the four rows in the table. The values in the output column are determined from applying the corresponding input values to the functional operator. For the AND truth table in Figure 2.5(a), F = 1 only when x and y are both 1, otherwise, F = 0. For the OR truth table in Figure 2.5(b), F = 1 when either x or y or both is a 1, otherwise F = 0. For the NOT truth table, the output F is just the inverted value of the input x.

F = xy

F = x' $F = \overline{x}$

| x | у   | F | x | у   | F |   |    |

|---|-----|---|---|-----|---|---|----|

| 0 | 0   | 0 | 0 | 0   | 0 | x | F  |

| 0 | 1   | 0 | 0 | 1   | 1 | 0 | 1  |

| 1 | 0   | 0 | 1 | 0   | 1 | 1 | 0  |

| 1 | 1   | 1 | 1 | 1   | 1 |   |    |

|   |     |   |   |     |   |   |    |

|   | (a) |   |   | (b) |   | ( | c) |

Figure 2.5 Truth tables for the three basic logical operators: (a) AND; (b) OR; (c) NOT.

Using a truth table is one method to formally describe the operation of a circuit or function. The truth table for any given logic expression (no matter how complex it is) can always be derived. Examples on the use of truth tables to describe digital circuits are given in the following sections. Another method to formally describe the operation of a circuit is by using Boolean expressions or Boolean functions.

### 2.5 Boolean Algebra and Boolean Functions

#### 2.5.1 Boolean Algebra

George Boole, in 1854, developed a system of mathematical logic, which we now call **Boolean algebra**. Based on Boole's idea, Claude Shannon, in 1938, showed that circuits built with binary switches can easily be described using Boolean algebra. The abstraction from switches being on and off to the use of Boolean algebra is as follows. Let  $B = \{0, 1\}$  be the Boolean algebra whose elements are one of the two values, 0 and 1. We define the operations AND (•), OR (+), and NOT (') for the elements of *B* by the axioms in Figure 2.6(a). These axioms are simply the definitions for the AND, OR, and NOT operators.

A variable x is called a **Boolean variable** if x takes on only values in B (i.e., either 0 or 1). Consequently, we obtain the theorems in Figure 2.6(b) for single variable and Figure 2.6(c) for two and three variables.

The theorems in Figure 2.6(b) can be proven easily by substituting the binary values into the expressions and using the axioms. For example, to show that Theorem 6a is true, we substitute 0 into x to get Axiom 3a, and substitute 1 into x to get Axiom 2a.

To prove the theorems in Figure 2.6(c), we can use either one of two methods: (1) use a truth table, or (2) use axioms and theorems that have already been proven. We show these two methods in the following two examples.

| 1a. | $0 \bullet 0 = 0$               | 1b. | 1 + 1 = 1         |

|-----|---------------------------------|-----|-------------------|

| 2a. | $1 \bullet 1 = 1$               | 2b. | 0 + 0 = 0         |

| 3a. | $0 \bullet 1 = 1 \bullet 0 = 0$ | 3b. | 1 + 0 = 0 + 1 = 1 |

| 4a. | 0' = 1                          | 4b. | 1' = 0            |

(a)

| 5a. | $x \bullet 0 = 0$               | 5b. | x + 1 = 1         | Null Element      |

|-----|---------------------------------|-----|-------------------|-------------------|

| ба. | $x \bullet 1 = 1 \bullet x = x$ | 6b. | x + 0 = 0 + x = x | Identity          |

| 7a. | $x \bullet x = x$               | 7b. | x + x = x         | Idempotent        |

| 8a. | (x')' = x                       |     |                   | Double Complement |

| 9a. | $x \bullet x' = 0$              | 9b. | x + x' = 1        | Inverse           |

| (b) |

|-----|

| 10a. | $x \bullet y = y \bullet x$                         | 10b. | x + y = y + x                                 | Commutative  |

|------|-----------------------------------------------------|------|-----------------------------------------------|--------------|

| 11a. | $(x \bullet y) \bullet z = x \bullet (y \bullet z)$ | 11b. | (x + y) + z = x + (y + z)                     | Associative  |

| 12a. | $x \bullet (y + z) = (x \bullet y) + (x \bullet z)$ | 12b. | $x + (y \bullet z) = (x + y) \bullet (x + z)$ | Distributive |

| 13a. | $x \bullet (x + y) = x$                             | 13b. | $x + (x \bullet y) = x$                       | Absorption   |

| 14a. | $(x \bullet y) + (x \bullet y') = x$                | 14b. | $(x+y) \bullet (x+y') = x$                    | Combining    |

|  | 15a. | $(x \bullet y)' = x' + y'$ | 15b. | $(x+y)' = x' \bullet y'$ | DeMorgan's |

|--|------|----------------------------|------|--------------------------|------------|

|--|------|----------------------------|------|--------------------------|------------|

(c)

Figure 2.6 Boolean algebra axioms and theorems: (a) axioms; (b) single-variable theorems; (c) two- and three-variable theorems.

**Example 2.1**: Proof of theorem using a truth table.

Prove Theorem 12a from Figure 2.6(c), using a truth table.

Theorem 12a states that  $x \bullet (y + z) = (x \bullet y) + (x \bullet z)$ . To prove that Theorem 12a is true using a truth table, we need to show that, for every combination of values for the three variables x, y, and z, the left-hand side of the expression is equal to the right-hand side.

We start with the first three columns labeled *x*, *y*, and *z*; and we enumerate all possible combinations of values for these three variables giving us the eight rows as shown next.

| x | у | z | (y + z) | $(x \bullet y)$ | $(x \bullet z)$ | $x \bullet (y+z)_{\bigcirc}$ | $(x \bullet y) + (x \bullet z)$ |

|---|---|---|---------|-----------------|-----------------|------------------------------|---------------------------------|

| 0 | 0 | 0 | 0       | 0               | 0               | 0 🖉                          | 0                               |

| 0 | 0 | 1 | 1       | 0               | 0               | 0                            |                                 |

| 0 | 1 | 0 | 1       | 0               | 0               | 0                            | <sup>م</sup> ري 0               |

| 0 | 1 | 1 | 1       | 0               | 0               | $\sim 0$                     | >>> 0                           |

| 1 | 0 | 0 | 0       | 0               | 0               |                              | Ø 0                             |

| 1 | 0 | 1 | 1       | 0               | 1               |                              | 1                               |

| 1 | 1 | 0 | 1       | 1               | 0               |                              | 1                               |

| 1 | 1 | 1 | 1       | 1               | 1               | 1                            | 1                               |

|   |   |   |         |                 |                 |                              |                                 |

For each combination (row), we evaluate the intermediate expressions (y + z),  $(x \bullet y)$ , and  $(x \bullet z)$  by substituting the values of x, y, and z into the expression. Finally, we obtain the values for the last two columns, which correspond to the left-hand side and right-hand side of Theorem 12a. The values in these two columns are identical for every combination of x, y, and z; therefore, we can say that Theorem 12a is true.

Example 2.2: Proof of theorem using axioms and theorems.

Prove Theorem 13b from Figure 2.6 (using other axioms and theorems from the figure.

Theorem 13b states that  $x + (x \bullet y)$  To prove that Theorem 13b is true using other axioms and theorems, we can argue as follows:

| by Identity Theorem 6a      |

|-----------------------------|

| by Distributive Theorem 12a |

| by Null element Theorem 5b  |

| by Identity Theorem 6a      |

|                             |

Example 2.2 shows that some theorems can be derived from others that already have been proven with the truth table. Full treatment of Boolean algebra is beyond the scope of this book and can be found in the references. For our purposes, we simply assume that all of the theorems are true and will use them just to show that two circuits are equivalent, as depicted in the next two examples.

Example 2.3: Using Boolean algebra to reduce an equation

Use Boolean algebra to reduce the equation F(x,y,z) = (x' + y' + x'y' + xy)(x' + yz) as much as possible.

$$F = (x' + y' + x'y' + xy) (x' + yz)$$

٠

٠

| $= (x' \bullet 1 + y' \bullet 1 + x'y' + xy) (x' + yz)$                  | by Identity Theorem 6a      |

|--------------------------------------------------------------------------|-----------------------------|

| = (x'(y + y') + y'(x + x') + x'y' + xy)(x' + yz)                         | by Inverse Theorem 9b       |

| = (x'y + x'y' + y'x + y'x' + x'y' + xy) (x' + yz)                        | by Distributive Theorem 12a |

| $= (x'y + x'y' + y'x + \frac{y'x'}{y'} + \frac{x'y'}{y'} + xy)(x' + yz)$ | by Idempotent Theorem 7b    |

| = (x'(y + y') + x(y + y'))(x' + yz)                                      | by Distributive Theorem 12a |

| $= (x' \bullet 1 + x \bullet 1) (x' + yz)$                               | by Inverse Theorem 9b       |

| = (x'+x) (x'+yz)                                                         | by Identity Theorem 6a      |

| = 1 (x' + yz)                                                            | by Inverse Theorem 9b       |

| =(x'+yz)                                                                 | by Identity Theorem 6a      |

Since the expression (x' + y' + x'y' + xy) (x' + yz) reduces down to (x' + yz), therefore, we do want to implement the circuit for the latter expression rather than the former because the circuit size for the latter is much smaller.

Example 2.4: Using Boolean algebra to show that two equations are equivalent

Show, using Boolean algebra, that the two equations

$$F_1 = (xy' + x'y + x' + y' + z') (x + y' + z)$$

and

$F_2 = y' + x'z + xz'$

are equivalent.

$$\begin{split} F_1 &= (xy' + x'y + x' + y' + z') (x + y' + z) \\ &= xy'x + xy'y' + xy'z + x'yy + x'yz + x'x + x'y' + x'z + y'x + y'y' + y'z + z'x + z'y' + z'z \\ &= xy' + xy' + xy'z + 0 + 0 + x'yz + 0 + x'y' + x'z + xy' + y' + y'z + xz' + y'z' + 0 \\ &= xy' + xy'z + x'yz + x'y' + x'z + y' + y'z + xz' + y'z' \\ &= y'(x + xz + x' + 1 + z + z') + x'z(y + 1) + xz' \\ &= y' + x'z + xz' \\ &= F_2 \end{split}$$

#### 2.5.2 \* Duality Principle

Notice in Figure 2.6 that we have listed the axioms and theorems in pairs. Specifically, we define the **dual** of a logic expression as one that is obtained by changing all + operators with  $\bullet$  operators, and vice versa, and by changing all 0's with 1's, and vice versa. For example, the dual of the logic expression:

$$(x \bullet y' \bullet z) + (x \bullet y \bullet z') + (y \bullet z) + 0$$

is

$$(x+y'+z) \bullet (x+y+z') \bullet (y+z) \bullet 1$$

The **duality principle** states that if a Boolean expression is true, then its dual is also true. Be careful in that it does not say that a Boolean expression is equivalent to its dual. For example, Theorem 5a in Figure 2.6(b) says that  $x \bullet 0 = 0$  is true, thus by the duality principle, its dual, x + 1 = 1 is also true. However,  $x \bullet 0 = 0$  is not equal to x + 1 = 1, since 0 definitely is not equal to 1.

We will see in Section 2.5.3 that the inverse of a Boolean expression easily can be obtained by first taking the dual of that expression and then complementing each Boolean variable in the resulting dual expression. In this respect, the duality principle is often used in digital logic design. Whereas an expression might be complex to implement, its inverse might be simpler, thus resulting in a smaller circuit; inverting the final output of this circuit will produce the same result as from the original expression.

#### 2.5.3 Boolean Functions and their Inverses

As we have seen, any digital circuit can be described by a logical expression, also known as a **Boolean** function. Any Boolean functions can be formed from binary variables and the Boolean operators  $\bullet$ , +, and ' (for AND, OR, and NOT, respectively). For example, the following Boolean function uses the three variables or literals *x*, *y*, and *z*. It has three AND terms (also referred to as **product terms**), and these AND terms are ORed (summed)

together. The first two AND terms each contain all three variables, while the last AND term contains only two variables. By definition, an AND (or product) term is either a single variable or two or more variables ANDed together. Quite often, we refer to functions that are in this format as a **sum-of-products** or **or-of-ands**.

Three AND Terms

$$F(x,y,z) = x \dot{y}' z + x y z' + y$$

Three Variables True Variables

Three Variables Two Variables

The value of a function evaluates to either 0 or 1, depending on the given set of values for the variables. For example, the function in the above figure evaluates to 1 when any one of the three AND terms evaluate to a 1, since 1 OR x is 1. The first AND term, xy'z, equals 1 if

$$x = 1, y = 0, and z = 1$$

because, if we substitute these values for x, y, and z into the first AND term xy'z, we get a 1. Similarly, the second AND term, xyz', equals 1 if

x = 1, y = 1, and z = 0

The last AND term, yz, has only two variables. What this means is that the value of this term is not dependent on the missing variable x. In other words, x can be either 0 or 1, but as long as y = 1 and z = 1, this term will be equal to 1.

Thus, we can summarize by saying that F evaluates to 1 if

$$x = 1, y = 0, and z = 1$$

or

$$x = 1, y = 1, and z = 0$$

or

$$x = 0, y = 1, and z = 1$$

or

$$x = 1, y = 1, and z = 1.$$

Otherwise, *F* evaluates to 0.

It is often more convenient to summarize this verbal description of a function with a truth table, as shown in Figure 2.7 under the column labeled F. Notice that the four rows in the table, where F = 1, match the four cases in the description.

| x | у | z | F | F' |

|---|---|---|---|----|

| 0 | 0 | 0 | 0 | 1  |

| 0 | 0 | 1 | 0 | 1  |

| 0 | 1 | 0 | 0 | 1  |

| 0 | 1 | 1 | 1 | 0  |

| 1 | 0 | 0 | 0 | 1  |

| 1 | 0 | 1 | 1 | 0  |

| 1 | 1 | 0 | 1 | 0  |

| 1 | 1 | 1 | 1 | 0  |

**Figure 2.7** Truth table for the function F = xy'z + xyz' + yz

The inverse of a function, denoted by F', can be obtained easily from the truth table for F by simply changing all the 0's to 1's and 1's to 0's, as shown in the truth table in Figure 2.7 under the column labeled F'. Therefore, we can write the Boolean function for F' in the sum-of-products format, where the AND terms are obtained from those rows where F' = 1. Thus, we get

F' = x'y'z' + x'y'z + x'yz' + xy'z'

To deduce F' algebraically from F requires the use of DeMorgan's theorem (Theorem 15a in Figure 2.6(c)) twice. For example, using the same function

F = xy'z + xyz' + yz

we obtain F' as follows

$$F' = (xy'z + xyz' + yz)' = (xy'z)' \bullet (xyz')' \bullet (yz)' = (x' + y + z') \bullet (x' + y' + z) \bullet (y' + z')$$

There are three things to notice about this equation for F'. First, F' is just the dual of F (as defined in Section 2.5.2) with all the variables inverted. Second, instead of being in a sum-of-products format, it is in a **product-of-sums (and-of-ors)** format where three OR terms (also referred to as "sum" terms) are ANDed together. Third, from the same original function F, we obtained two different equations for F'. From the truth table in Figure 2.7, we obtained

$$F' = x'y'z' + x'y'z + x'yz' + xy'z'$$

and from applying DeMorgan's Theorem to F, we obtained

$$F' = (x' + y + z') \bullet (x' + y' + z) \bullet (y' + z')$$

Hence, we must conclude that these two expressions for F', where one is in the sum-of-products format and the other is in the product-of-sums format, are equivalent. In general, all functions can be expressed in either the sum-of-products or product-of-sums format.

Thus, we should also be able to express the same function, F = xy'z + xyz' + yz, in the product-of-sums format. We can derive it using one of two methods. For method one, we can start with F' and apply DeMorgan's theorem to it just like how we obtained F' from F.

$$F = (F')' = (x'y'z' + x'y'z + x'yz' + xy'z')' = (x'y'z')' \bullet (x'y'z)' \bullet (x'yz')' \bullet (xy'z')' = (x + y + z) \bullet (x + y + z') \bullet (x + y' + z) \bullet (x' + y + z)$$

For the second method, we start with the original F and convert it to the product-of-sums format using the Boolean theorems from Figure 2.6.

| F = xy'z + xyz' + yz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| $= (x+x+y) \bullet (x+x+z) \bullet (x+y+y) \bullet (x+y+z) \bullet (x+z'+y) \bullet (x+z'+z) \bullet$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (Step 1)    |

| $(y'+x+y) \bullet (y'+x+z) \bullet (y'+y+y) \bullet (y'+y+z) \bullet (y'+z'+y) \bullet (y'+z'+z) \bullet$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

| $(z+x+y) \bullet (z+x+z) \bullet (z+y+y) \bullet (z+y+z) \bullet (z+z'+y) \bullet (z+z'+z)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

| $= (x+y) \bullet (x+z) \bullet (x+y) \bullet (x+y+z) \bullet (x+z'+y) \bullet (y'+x+z) \bullet (z+x+y) \bullet (z+x) \bullet (z+y) \bullet (z+y)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (Step 2)    |

| $= (x+y) \bullet (x+z) \bullet (x+y+z) \bullet (x+y+z') \bullet (x+y'+z) \bullet (y+z)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (Step 3)    |

| $= (x+y+zz') \bullet (x+yy'+z) \bullet (x+y+z) \bullet (x+y+z') \bullet (x+y'+z) \bullet (xx'+y+z)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (Step 4)    |

| $= (x+y+z) \bullet (x+y+z') \bullet (x+y+z) \bullet (x+y'+z) \bullet (x+y+z) \bullet (x+y+z') \bullet (x+y'+z) \bullet (x+y+z') \bullet (x+y+z) \bullet (x'+y+z) \bullet $ | z) (Step 5) |

| $= (x+y+z) \bullet (x+y+z') \bullet (x+y'+z) \bullet (x'+y+z)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

In Step 1, we apply Theorem 12b (Distributive) to get every possible combination of the sum terms. For example, the first sum term (x + x + y) is obtained from getting the first x from xy'z, the second x from xyz', and the y from yz. The second sum term (x + x + z) is obtained from getting the first x from xy'z, the second x from xyz', and the z from yz. This is repeated for all combinations. In this step, the sum terms, such as (x + z' + z), where it contains variables of the form v + v', can be eliminated, since v + v' = 1, and  $1 \cdot x = x$ .

In Step 2 and Step 3, duplicate variables and terms are eliminated. For example, the term (x + x + y) is equal to (x + y + y), which is just (x + y). The term (x + z' + z) is equal to (x + 1), which is equal to just 1, and therefore, can be eliminated completely from the expression.

In Step 4, every sum term with a missing variable will have that variable added back in by using Theorems 6b and 9a, which says that x + 0 = x and yy' = 0, therefore, x + yy' = x.

Step 5 uses the Distributive Theorem, and the resulting duplicate terms are again eliminated to give us the format that we want.

Functions that are in the product-of-sums format (such as the one shown below) are more difficult to deduce when they evaluate to 1. For example, using

$$F' = (x' + y + z') \bullet (x' + y' + z) \bullet (y' + z')$$

F' evaluates to 1 when all three terms evaluate to 1. For the first term to evaluate to 1, x can be 0, y can be 1, or z can be 0. For the second term to evaluate to 1, x can be 0, y can be 0, or z can be 1. Finally, for the last term, y can be 0, z can be 0, or x can be either 0 or 1. As a result, we end up with many more combinations to consider, even though many of the combinations are duplicates.

However, it is easier to determine when a product-of-sums format expression evaluates to 0. For example, using the same expression:

$$F' = (x' + y + z') \bullet (x' + y' + z) \bullet (y' + z')$$

F' evaluates to 0 when any one of the three OR terms is 0, since 0 AND x is 0; and this happens when

x = 1, y = 0, and z = 1 for the first OR term,

or

x = 1, y = 1, and z = 0 for the second OR term,

or

y = 1, z = 1, and x can be either 0 or 1 for the last OR term.

Similarly, for a sum-of-products format expression, it is easy to evaluate when it is a 1 but difficult to evaluate when it is a 0.

These four conditions in which F' evaluates to 0 match exactly the four rows in the truth table shown in Figure 2.7 where F' = 0. Therefore, we see that, in general, the unique algebraic expression for any Boolean function can be specified by either (1) selecting the rows from the truth table where the function is a 1 and using the sum-of-products format, or (2) selecting the rows from the truth table where the function is a 0 and using the product-of-sums format. Whatever format we decide to use, the one thing to remember is that we are always interested in only when the function (or its inverse) is equal to a 1.

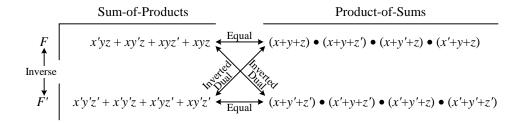

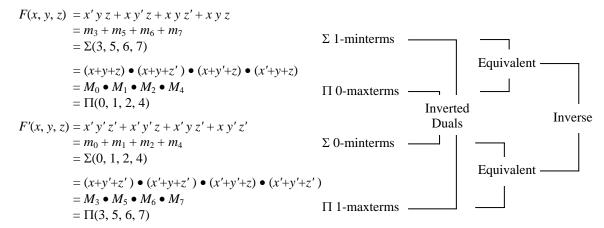

Figure 2.8 summarizes these two formats for the function F = xy'z + xyz' + yz and its inverse F'. Notice that the sum-of-products format for F is the dual with its variables inverted from the product-of-sums format for F'. Similarly, the product-of-sums format for F is the dual with its variables inverted from the sum-of-products format for F'.

**Figure 2.8** Relationships between the function F = xy'z + xyz' + yz and its inverse F', and between the sum-ofproducts and product-of-sums formats. The label "Inverted Dual" means applying the duality principle and then inverting the variables.

#### 2.6 Minterms and Maxterms

As you recall, a product term is a term with either a single variable or two or more variables ANDed together, whereas, a sum term is a term with either a single variable or two or more variables ORed together. To differentiate

between a term that contains any number of variables with a term that contains all the variables used in the function, we use the words minterm and maxterm. We are not introducing new ideas here; rather, we are just introducing two new words and notations for defining what we have already learned.

### 2.6.1 Minterms

A minterm is a product term that contains all the variables used in a function. For a function with *n* variables, the notation  $m_i$ , where  $0 \le i < 2^n$ , is used to denote the minterm whose index *i* is the binary value of the *n* variables, such that the variable is complemented if the value assigned to it is a 0 and uncomplemented if it is a 1.

For example, for a function with three variables x, y, and z, the notation  $m_3$  is used to represent the term in which the values for the variables xyz are 011 (for the subscript 3). Since we want to complement the variable whose value is a 0 and uncomplement it if it is a 1, therefore,  $m_3$  is for the minterm x'yz. Figure 2.9(a) shows the eight minterms and their notations for n = 3 using the three variables x, y, and z.

When specifying a function, we usually start with product terms that contain all of the variables used in the function. In other words, we want the sum of minterms, and more specifically, the sum of the one-minterms (i.e., the minterms for which the function is a 1) as opposed to the zero-minterms (i.e., the minterms for which the function is a 0). We use the notation **1-minterm** to denote one-minterm, and **0-minterm** to denote dero-minterm.

| x | у | z | Minterm | Notation |

|---|---|---|---------|----------|

| 0 | 0 | 0 | x'y'z'  | $m_0$    |

| 0 | 0 | 1 | x'y'z   | $m_1$    |

| 0 | 1 | 0 | x' y z' | $m_2$    |

| 0 | 1 | 1 | x'yz    | $m_3$    |

| 1 | 0 | 0 | x y' z' | $m_4$    |

| 1 | 0 | 1 | x y' z  | $m_5$    |

| 1 | 1 | 0 | x y z'  | $m_6$    |

| 1 | 1 | 1 | x y z   | $m_7$    |

| ۱. |

|----|

| ,  |

|    |

| x | y        | z        | Maxterm                   | Notation   |

|---|----------|----------|---------------------------|------------|

| 0 | 0        | 0        | x + y + z                 | $M_0$      |

| 0 | 0        | 1        | x + y + z'                | $M_1$      |

| 0 | 1        | 0        | x + y' + z                | $\sim M_2$ |

| 0 | 1        | 1        | $x + y' + z^{\mathbb{V}}$ | $M_3$      |

| 1 | 0        | $\delta$ | x + y + z                 | $M_4$      |

| 1 | 0        | 1        | x' + y' + z'              | $M_5$      |

| 1 | 1        | Ø        | x' + y' + z               | $M_6$      |

| 1 | 1        | V        | x + y' + z'               | $M_7$      |

|   | $( \cap$ |          |                           |            |

/h

(b)

Figure 2.9 (a) Minterms for three variables. (b) Maxterms for three variables.

The function from the previous section:

$$F = xy'z + xyz' + yz$$

= x'yz + xy'z + xyz' + xyz

and repeated in the following truth table has the 1-minterms:  $m_3$ ,  $m_5$ ,  $m_6$ , and  $m_7$ .

|     | x  | y         | <i>z</i> ( | Å   | F | <sup>9</sup> Minterm | Notation |  |  |  |  |

|-----|----|-----------|------------|-----|---|----------------------|----------|--|--|--|--|

|     | 0  | $\otimes$ | $0^{0}$    |     | A | x'y'z'               | $m_0$    |  |  |  |  |

|     | 0  | 0         | S A        | Q.  | 4 | x'y'z                | $m_1$    |  |  |  |  |

|     | 0  |           | 0          | Ø   | 1 | x'yz'                | $m_2$    |  |  |  |  |

|     | 04 | Ţ         | ×          | ° 1 | 0 | x'yz                 | $m_3$    |  |  |  |  |

|     |    |           | Ũ          | 0   | 1 | x y' z'              | $m_4$    |  |  |  |  |

| _(( | fr | 0         | )]         | 1   | 0 | x y' z               | $m_5$    |  |  |  |  |

| R   |    | )1        | Ø          | 1   | 0 | x y z'               | $m_6$    |  |  |  |  |

|     | X  | S.        | 1          | 1   | 0 | x y z                | $m_7$    |  |  |  |  |

|     | 1) | ¥/        |            |     |   |                      |          |  |  |  |  |

Thus, a shorthand notation for the function is

$$F(x, y, z) = m_3 + m_5 + m_6 + m_7$$

By using just the minterm notations, we do not know how many variables are in the original function. Consequently, we need to explicitly specify the variables used by the function, as in F(x, y, z). We can further simplify the notation by using the standard algebraic symbol  $\Sigma$  for summation and listing out the minterm index numbers. Therefore, we have

$F(x, y, z) = \Sigma(3, 5, 6, 7)$

These are just different ways of expressing the same function.

Since a function is obtained from the sum of the 1-minterms, the inverse of the function, therefore, must be the sum of the 0-minterms. This can be obtained easily by replacing the set of indices with those that were excluded from the original set. Therefore,

$F'(x, y, z) = \Sigma(0, 1, 2, 4)$

Example 2.5: Converting a function to the sum-of-minterms format using Boolean algebra

Given the Boolean function F(x, y, z) = y + x'z, use Boolean algebra to convert the function to the sum-ofminterms format.

This function has three variables. In a sum-of-minterms format, all product terms must have all variables. To do so, we need to expand each product term by ANDing it with (v + v') for every missing variable v in that term. Since (v + v') = 1, ANDing a product term with (v + v') does not change the value of the term.

F = y + x'z= y(x+x')(z+z') + x'z(y+y') expand 1<sup>st</sup> term by ANDing it with (x+x')(z+z'), and 2<sup>nd</sup> term with (y+y')=  $xyz + xyz' + x'yz + x'yz' + \frac{x'yz}{x'} + x'y'z$ =  $m_7 + m_6 + m_3 + m_2 + m_1$ =  $\Sigma(1, 2, 3, 6, 7)$  sum of 1-minterms

Example 2.6: Converting the inverse of a function to the sum-of-minterms format

Given the Boolean function F(x, y, z) = y + x'z, use Boolean algebra to convert the inverse of the function to the sum-of-minterms format.

| F' = (y + x'z)'<br>= y' • (x'z)'<br>= y' • (x+z')<br>= y'x + y'z'<br>= y'x(z+z') + y'z' (x+x')<br>= xy'z + xy'z' + xy'z' + x'y'z'<br>= m_5 + m_4 + m_0 | inverse<br>use DeMorgan<br>use DeMorgan<br>use Distributive Theorem to change to sum of products format<br>expand 1 <sup>st</sup> term by ANDing it with $(z+z')$ , and 2 <sup>nd</sup> term with $(x+x')$ |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| $=\Sigma(0, 4, 5)$                                                                                                                                     | sum of 0-minterms                                                                                                                                                                                          | • |

### 2.6.2 \* Maxterms

Analogous to a minterm, a **maxterm** is a sum term that contains all of the variables used in the function. For a function with *n* variables, the notation  $M_i$ , where  $0 \le i < 2^n$ , is used to denote the maxterm whose index *i* is the binary value of the *n* variables, such that the variable is complemented if the value assigned to it is a 1 and uncomplemented if it is a 0.

For example, for a function with three variables x, y, and z, the notation  $M_3$  is used to represent the term in which the values for the variables xyz are 011 (for the subscript 3). For maxterms, we want to complement the variable whose value is a 1 and uncomplement it if it is a 0, hence,  $M_3$  is for the maxterm x + y' + z'. Figure 2.9(b) shows the eight maxterms and their notations for n = 3 using the three variables x, y, and z.

We have seen that a function can also be specified as a product-of-sums, or more specifically, a **product of 0-maxterms** (i.e., the maxterms for which the function is 0. Just like the minterms, we use the notation **1-maxterm** to denote one-maxterm, and **0-maxterm** to denote zero-maxterm. Thus, the function:

F(x, y, z) = xy'z + xyz' + yz

$$= (x + y + z) \bullet (x + y + z') \bullet (x + y' + z) \bullet (x' + y + z)$$

which is shown in the following table

| x | у | z | F | F' | Maxterm      | Notation |

|---|---|---|---|----|--------------|----------|

| 0 | 0 | 0 | 0 | 1  | x + y + z    | $M_0$    |

| 0 | 0 | 1 | 0 | 1  | x + y + z'   | $M_1$    |

| 0 | 1 | 0 | 0 | 1  | x + y' + z   | $M_2$    |

| 0 | 1 | 1 | 1 | 0  | x + y' + z'  | $M_3$    |

| 1 | 0 | 0 | 0 | 1  | x' + y + z   | $M_4$    |

| 1 | 0 | 1 | 1 | 0  | x' + y + z'  | $M_5$    |

| 1 | 1 | 0 | 1 | 0  | x' + y' + z  | $M_6$    |

| 1 | 1 | 1 | 1 | 0  | x' + y' + z' | $M_7$    |

can be specified as the product of the 0-maxterms  $M_0$ ,  $M_1$ ,  $M_2$ , and  $M_4$ . The shorthand notation for the function is

$$F(x, y, z) = M_0 \bullet M_1 \bullet M_2 \bullet M_4$$

By using the standard algebraic symbol  $\Pi$  for product and listing out the maxterms index numbers, the notation is further simplified to

$F(x, y, z) = \Pi(0, 1, 2, 4)$

The following summarizes these relationships for the function F = xy'z + xyz' + yz and its inverse. Comparing these equations with those in Figure 2.8, we see that they are identical.

Notice that it is always the  $\Sigma$  of minterms and  $\Pi$  of maxterms; you never have  $\Sigma$  of maxterms or  $\Pi$  of minterms.

Example 2.7: Converting a function to the product-of-maxterms format

Given the Boolean function F(x, y, z) = y + x'z, use Boolean algebra to convert the function to the product-of-maxterms format.

To change a sum term to a maxterm, we expand each term by ORing it with (vv') for every missing variable v in that term. Since (vv') = 0, therefore, ORing a sum term with (vv') does not change the value of the term.

F = y + x'z = y + (x'z) = (y+x')(y+z) use Distributive Theorem to change to product of sums format = (y+x'+zz')(y+z+xx') expand 1<sup>st</sup> term by ORing it with zz', and 2<sup>nd</sup> term with xx' = (x'+y+z)(x'+y+z')(x+y+z) (x'+y+z)  $= M_4 \bullet M_5 \bullet M_0$  $= \Pi(0, 4, 5)$  product of 0-maxterms

٠

٠

Example 2.8: Converting the inverse of a function to the product-of-maxterms format

Given the Boolean function F(x, y, z) = y + x'z, use Boolean algebra to convert the inverse of the function to the product-of-maxterms format.

F' = (y + x'z)'inverse  $= y' \bullet (x'z)'$ use DeMorgan  $= y' \bullet (x+z')$ use DeMorgan  $= (y' + xx' + zz') \bullet (x+z' + yy')$ expand 1<sup>st</sup> term by ORing it with xx' + zz', and 2<sup>nd</sup> term with yy'= (x+y'+z) (x+y'+z') (x'+y'+z) (x'+y'+z') (x+y+z') (x+y+z')  $= M_2 \bullet M_3 \bullet M_6 \bullet M_7 \bullet M_1$   $= \Pi(1, 2, 3, 6, 7)$ product of 1-maxterms

### 2.7 Canonical, Standard, and non-Standard Forms

Any Boolean function that is expressed as a sum-of-minterms, or as a product-of-maxterms is said to be in its **canonical form**. For example, the following two expressions are in their canonical forms:

$$F = x' y z + x y' z + x y z' + x y z$$

$$F' = (x+y'+z') \bullet (x'+y+z') \bullet (x'+y'+z) \bullet (x'+y'+z')$$

As noted from the previous section, to convert a Boolean function from one canonical form to its other equivalent canonical form, simply interchange the symbols  $\Sigma$  with  $\Pi$  and list the index numbers that were excluded from the original form. For example, the following two expressions are equivalent.

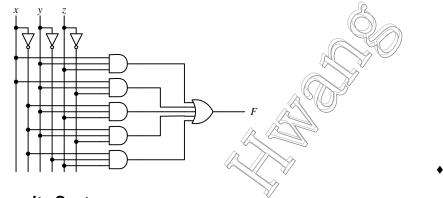

$F_1(x, y, z) = \Sigma(3, 5, 6, 7)$  $F_2(x, y, z) = \Pi(0, 1, 2, 4)$